# Architectures Matérielles et Systèmes d'Exploitation

## Transistors et Circuits Logiques

### 1 Un peu d'histoire

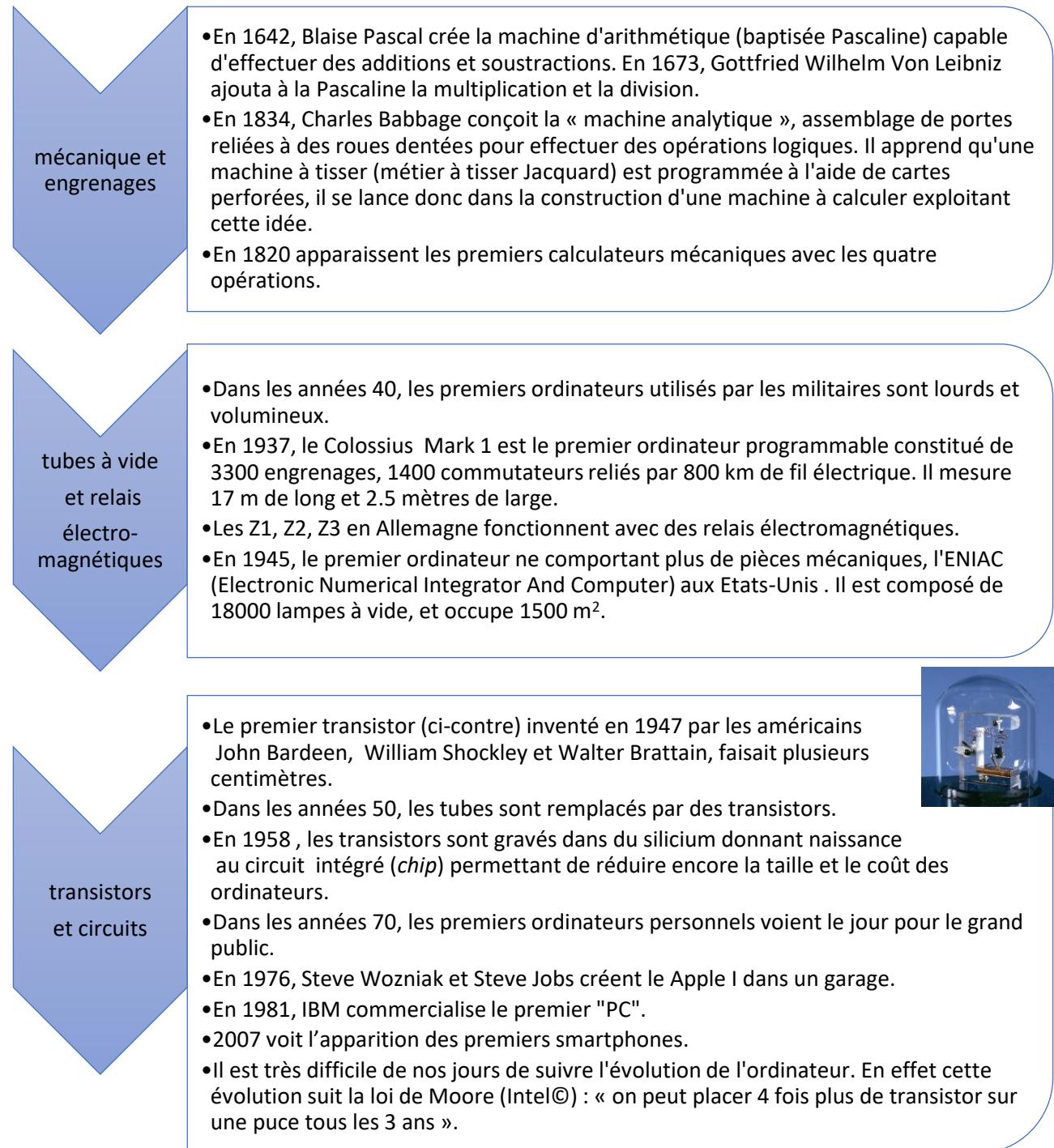

La composition des ordinateurs a évolué au cours du temps :

## 2 Transistors

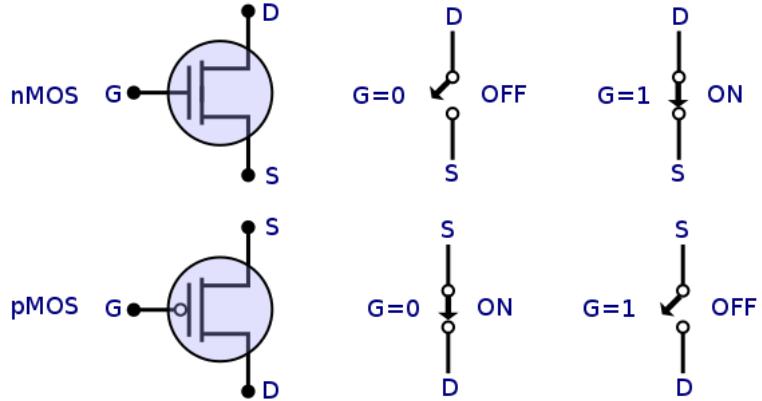

Un transistor est essentiellement un interrupteur électronique qui laisse passer un courant ou pas. Nous pouvons faire correspondre ces deux états aux deux chiffres 1 et 0 (ou aux valeurs booléennes True et False).

Il est composé de trois parties : une source S, une grille G et un drain D. La source et le drain sont soit connectés, soit déconnectés selon la valeur de la grille (0 ou 1).

Il existe plusieurs styles de transistors, voici deux des plus courants.

### Transistor NMOS :

- Si une tension positive ( 1 ) est appliquée à la grille le courant peut passer entre S et D.

- Si une tension nulle est appliquée à la grille ( 0 ) le courant ne peut pas passer entre S et D.

### Transistor PMOS :

- Si une tension positive ( 1 ) est appliquée à la grille le courant ne peut pas passer entre S et D.

- Si une tension nulle ( 0 ) le courant peut passer.

Source : <https://en.wikichip.org/wiki/mosfet>

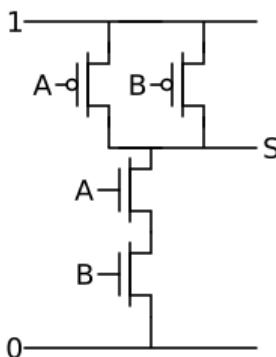

### Exercice 1.

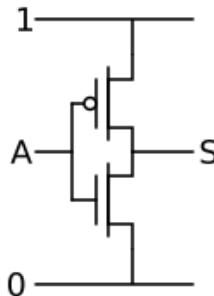

a) Compléter la table de vérité du montage électronique ci-contre.

| A | B | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

b) Compléter et comparer avec la table de vérité ci-dessous.

| A | B | A AND B | NOT (A AND B) |

|---|---|---------|---------------|

| 0 | 0 | 0       | 1             |

| 0 | 1 | 0       | 1             |

| 1 | 0 | 0       | 1             |

| 1 | 1 | 1       | 0             |

C'est l'opérateur NAND

### Exercice 2.

a) Compléter la table de vérité du montage électronique ci-contre

| A | S |

|---|---|

| 0 | 1 |

| 1 | 0 |

b) Déterminer l'opérateur booléen associé.

NOT A

### Transistor CMOS :

- C'est un mélange entre les technologies PMOS et NMOS. Tout circuit CMOS est divisé en deux parties : une intégralement composée de transistors PMOS et une autre de transistors NMOS.

### 3 Portes logiques

Comme dans l'exercice précédent, il est possible de fabriquer des composants à l'aide des transistors pour réaliser des opérations booléennes ou des opérations. On appelle ces circuits des **portes logiques**.

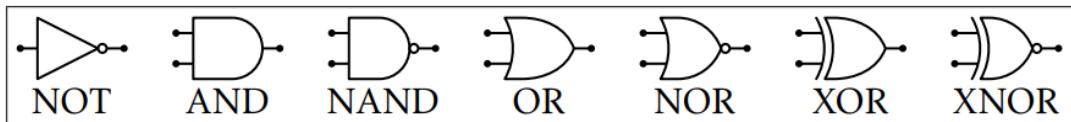

Les principales portes logiques sont les suivantes (en représentation classique dite américaine<sup>1</sup>):

Les portes **NAND** et **NOR** sont dites **universelles**, elles permettent chacune de fabriquer les autres portes logiques.

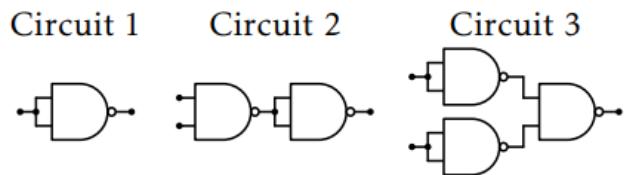

#### Exercice 3.

Déterminer quelles portes logiques ont été construites avec des portes NAND dans les trois circuits suivants.

Circuit 1 : NOT

Circuit 2 : AND

Circuit 3 : OR

### 4 Circuits combinatoires

Lorsqu'on assemble des portes logiques entre elles on peut obtenir des **circuits combinatoires** : ce sont des circuits électroniques qui comportent plusieurs entrées (généralement notées A, B, C ...) pour fournir un résultat en sortie. La **table de vérité** que l'on obtient correspond au tableau de valeurs d'une fonction booléenne.

Le circuit combinatoire est le terme "concret / électronique" alors que le terme fonction booléenne est le terme "théorique / mathématique".

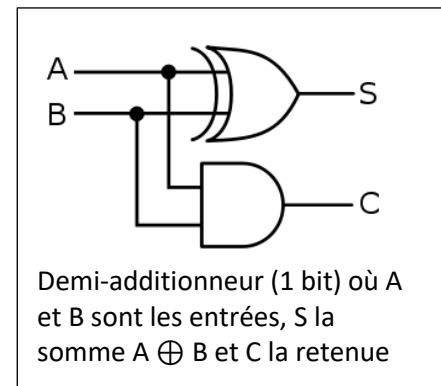

On peut par exemple construire le circuit ci-contre, appelé « demi-additionneur » .

Codée sur un bit, la table de vérité est :

| A | B | $A \oplus B$ | Retenue |

|---|---|--------------|---------|

| 0 | 0 | 0            | 0       |

| 0 | 1 | 1            | 0       |

| 1 | 0 | 1            | 0       |

| 1 | 1 | 0            | 1       |

Demi-additionneur (1 bit) où A et B sont les entrées, S la somme  $A \oplus B$  et C la retenue

#### Exercice 4.

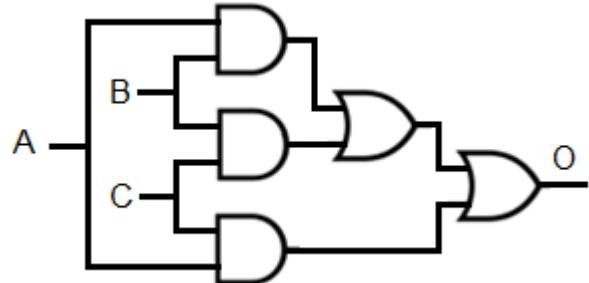

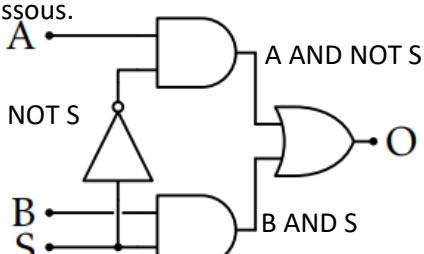

Compléter la table de vérité du circuit ci-dessous.

| A | B | S | A AND NOT S | B AND S | O |

|---|---|---|-------------|---------|---|

| 0 | 0 | 0 | 0           | 0       | 0 |

| 0 | 1 | 0 | 0           | 0       | 0 |

| 1 | 0 | 0 | 1           | 0       | 1 |

| 1 | 1 | 0 | 1           | 0       | 1 |

| 0 | 0 | 1 | 0           | 0       | 0 |

| 0 | 1 | 1 | 0           | 1       | 1 |

| 1 | 0 | 1 | 0           | 0       | 0 |

| 1 | 1 | 1 | 0           | 1       | 1 |

Ce circuit combinatoire est appelé « muxer », il permet de sélectionner la valeur à envoyer en sortie, entre les deux entrées A et B, en fonction de la valeur de S.

<sup>1</sup> En représentation « rectangulaire », dite « européenne » les portes sont représentées par des boîtes rectangulaires contenant le symbole de la porte.

### Exercice 5.

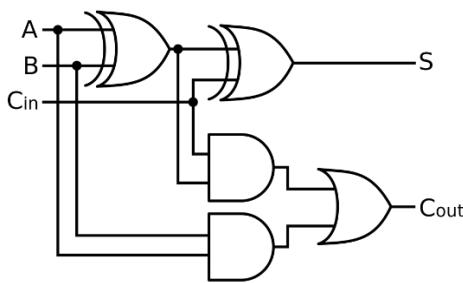

Compléter la table de vérité du circuit combinatoire suivant et déterminer l'opération binaire qu'il effectue.

C'est un additionneur avec retenue en entrée (Cin) et en sortie(Cout)

| A | B | C <sub>in</sub> | S | C <sub>out</sub> |

|---|---|-----------------|---|------------------|

| 0 | 0 | 0               | 0 | 0                |

| 0 | 0 | 1               | 1 | 0                |

| 0 | 1 | 0               | 1 | 0                |

| 0 | 1 | 1               | 0 | 1                |

| 1 | 0 | 0               | 1 | 0                |

| 1 | 0 | 1               | 0 | 1                |

| 1 | 1 | 0               | 0 | 1                |

| 1 | 1 | 1               | 1 | 1                |

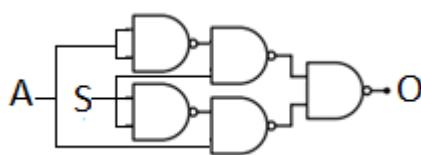

### Exercice 6.

Dessiner un circuit logique correspondant à la table ci-contre.

L'objectif est de renvoyer la valeur de A si S = 0 et de renvoyer (non A) sinon.

ou avec des NAND :

| A | S | O |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

### Exercice 7.

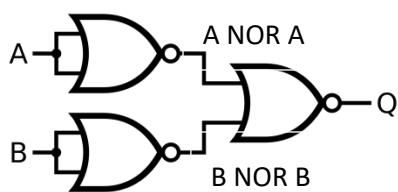

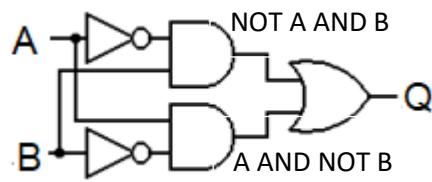

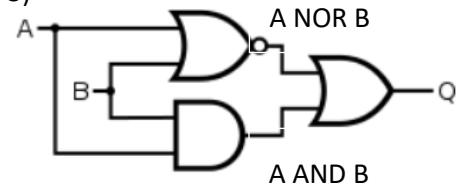

Compléter les tables de vérité des circuits combinatoires ci-dessous et déterminer l'opération binaire qu'ils effectuent.

1)

| A | B | A NOR A | B NOR B | Z |

|---|---|---------|---------|---|

| 0 | 0 | 1       | 1       | 0 |

| 0 | 1 | 1       | 0       | 0 |

| 1 | 0 | 0       | 1       | 0 |

| 1 | 1 | 0       | 0       | 1 |

On obtient A AND B

2)

| A | B | NOT A AND B | A AND NOT B | Q |

|---|---|-------------|-------------|---|

| 0 | 0 | 0           | 0           | 0 |

| 0 | 1 | 1           | 0           | 1 |

| 1 | 0 | 0           | 1           | 1 |

| 1 | 1 | 0           | 0           | 0 |

On obtient A XOR B

3)

| A | B | A NOR B | A AND B | Q |

|---|---|---------|---------|---|

| 0 | 0 | 1       | 0       | 1 |

| 0 | 1 | 0       | 0       | 0 |

| 1 | 0 | 0       | 0       | 0 |

| 1 | 1 | 0       | 1       | 1 |

On obtient A XNOR B

Il y a de nombreuses solutions pour les exercices suivants, en voilà un exemple pour chacune:

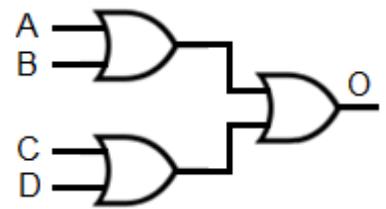

### Exercice 8.

Dessiner un circuit logique qui a 4 entrées A, B, C et D et dont la sortie O vaut 1 si et seulement si au moins une des entrées est non nulle.

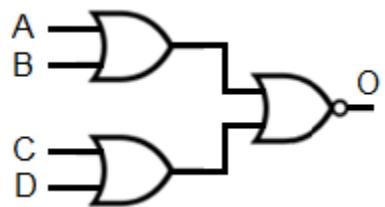

### Exercice 9.

Dessiner un circuit logique qui a 4 entrées A, B, C et D et dont la sortie O vaut 1 si et seulement si toutes les entrées sont nulles.

### Exercice 10.

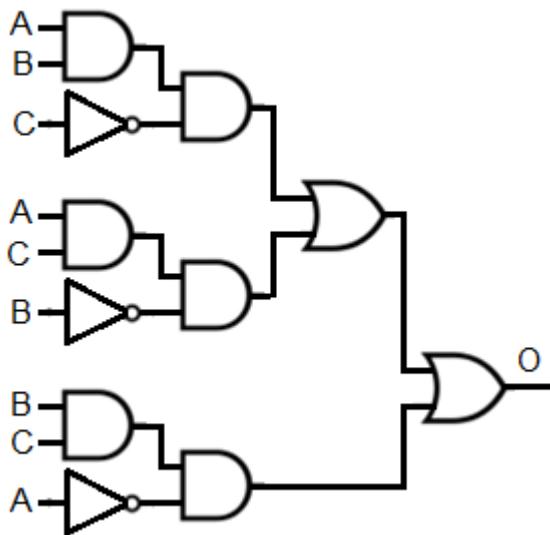

Dessiner un circuit logique qui a 3 entrées A, B et C et dont la sortie O vaut 1 si et seulement si exactement deux des entrées sont non nulles.

### Exercice 11.

Dessiner un circuit logique qui a 3 entrées A, B et C et dont la sortie O vaut 1 si et seulement si aux moins deux des entrées sont non nulles.